西门子推出 Tessent Multi-die 解决方案,实现 2.5D/3D IC 的可测试性设计自动化

西门子数字化工业软件近日推出 Tessent Multi-die 软件解决方案,旨在帮助客户加快和简化基于 2.5D 和 3D 架构的下一代集成电路 (IC) 关键可测试性设计 (DFT) 。

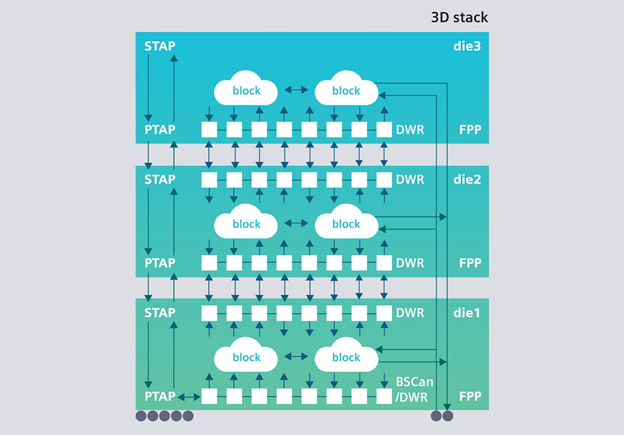

随着市场对于更小巧、更节能、更高性能的 IC 需求不断提升, IC 设计业也面临着严苛挑战。下一代组件更倾向于采用 2.5D 和 3D 架构,以垂直 (3D IC) 或并排 (2.5D) 的方式连接多个芯片,使其作为单一组件工作。然而,这样的方式对 IC 测试提出巨大挑战,大部分传统的测试方法都基于常规的 2D 工艺。

为了应对这些挑战,西门子推出 Tessent Multi-die —— 一款全面的 DFT 自动化解决方案,可处理与 2.5D 和 3D IC 设计有关的复杂DFT 任务。该解决方案可与西门子的 Tessent TestKompress Streaming Scan Network 软件和 Tessent IJTAG 软件配合使用,优化每个模块的 DFT 测试资源,无需担忧对设计其余部分造成影响,从而简化了 2.5D 和 3D IC 的 DFT 工作。现在, IC 设计团队只需使用 Tessent Multi-die 软件,就可以快速开发符合 IEEE 1838 标准的 2.5D 和3D IC 架构硬件。

西门子数字化工业软件副总裁兼 Tessent 业务部门总经理 Ankur Gupta 表示:“在 2.5D 和 3D 组件中采用高密度封装芯片设计的需求日益增多, IC 设计公司也面临着快速增加的 IC 测试复杂难题。借助于西门子的 Tessent Multi-die 解决方案,我们的客户能够为其未来设计做好充分准备,同时减少测试工作量,降低当前制造测试成本。”

除了支持 2.5D 和 3D IC 设计的全面测试之外,Tessent Multi-die 解决方案还可生成芯片间(die-to-die) 测试向量,并使用边界扫描描述语言 (BSDL) 实现封装级别测试。此外, Tessent Multi-die 可利用西门子 Tessent TestKompress Streaming Scan Network 软件的分组数据传输功能,支持灵活并行端口 (FPP) 技术的集成。于 2020 年推出的 Tessent TestKompress Streaming Scan Network 软件可将内核级 DFT 要求与芯片级测试交付资源分离,使用真实、有效且自下而上式的流程来实现 DFT ,从而简化 DFT 的规划和实施,同时将测试时间缩短 4 倍。

Pedestal Research 总裁兼研究总监 Laurie Balch 表示:“随着时间推移,传统的 2D IC 设计方法逐渐显露出局限性,越来越多的设计团队开始利用 2.5D 和 3D IC 架构,以满足其在功耗、性能以及尺寸等方面的要求。在新设计中部署这些高级架构的首要步骤就是制定 DFT 策略,来应对复杂架构带来的种种挑战,避免增加成本或延误产品上市时间。通过持续开发 DFT 技术,满足多维设计的需求, EDA 厂商将进一步促进 2.5D 和 3D 架构在全球范围的应用。”

上一篇:红帽在AWS Marketplace推出红帽Ansible自动化平台

栏 目:开发工具

本文标题:西门子推出 Tessent Multi-die 解决方案,实现 2.5D/3D IC 的可测试性设计自动化

本文地址:

您可能感兴趣的文章

- 10-24西门子推出 Tessent Multi-die 解决方案,实现 2.5D/3D IC 的可测试性设计自动化

- 03-11闲鱼如何建设技术舆情治理体系 (多图多代码)

- 09-21InEight专注于软件创新的标准化和基准更新

- 04-02一年增加 1.2w 星,Dapr 能否引领云原生中间件的未来?

- 10-20西门子宣布推出Solid Edge 2023

- 03-10云计算开发:Python练习实例-输入数值按规律插入数组

- 03-232B 领域下低代码的探索之路

- 10-26红帽在AWS Marketplace推出红帽Ansible自动化平台

- 10-12VMware推动云智能时代到来

- 03-07低代码平台四大常见用例开发

阅读排行

推荐教程

- 11-01阿里云无影升级2.0 云电脑解决方案时代到来

- 11-01阿里云数据库全面Serverless化!与AI共同驱动走向一站式智能数据平台

- 11-012023云栖大会关键词:开放、大模型、MaaS、产业智能升级

- 10-31Serverless化云产品超40款阿里云发布全球首款容器计算服务

- 10-31阿里云给中国所有大学生每人送一台云服务器

- 10-31解密杭州亚运背后科技:核心系统100%上云,20多项全球首创智能应用

- 10-312023云栖大会开幕 阿里巴巴蔡崇信:打造AI时代最开放的云

- 10-31巴黎奥运会将基于阿里云实现云上转播

- 10-31马斯克440亿美元收购Twitter一年后:全力“下云”,成本速降60%,功能代码从70万行减少至7万!

- 10-30中国广电已建700MHz基站59万站 5G用户突破1800万